module fulladder (sum, c_out, a, b, c_in);

wire s1, c1, c2;

output sum;

output c_out;

input a, b, c_in;

xor g1(s1, a, b);

xor g2(sum, s1, c_in);

and g3(c1, a,b);

and g4(c2, s1, c_in) ;

xor g5(c_out, c2, c1) ;

endmodule

module adder3(sum, c_out, a, b, c_in);

wire [2:0] c;

output [2:0] sum;

output c_out;

input [2:0] a;

input [2:0] b;

input c_in;

fulladder fa1(sum[0], c[1], a[0], b[0], c_in) ;

fulladder fa2(sum[1], c[2], a[1], b[1], c[1]) ;

fulladder fa3(sum[2], c_out, a[2], b[2], c[2]) ;

endmodule

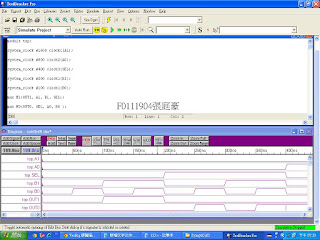

module main;

reg [2:0] a;

reg [2:0] b;

wire [2:0] sum;

wire c_out;

adder3 DUT (sum, c_out, a, b, 1'b0);

initial

begin

a = 4'b0101;

b = 4'b0000;

end

always #50 begin

b=b+1;

$monitor("%dns monitor: a=%d b=%d sum=%d", $stime, a, b, sum);

end

initial #2000 $finish;

endmodule