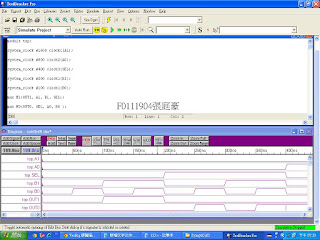

wire [2:0] A, B,out;

wire SEL;

system_clock #6400 clock1(SEL);

system_clock #3200 clock2(A[2]);

system_clock #1600 clock3(A[1]);

system_clock #800 clock34(A[0]);

system_clock #400 clock1(B[2]);

system_clock #200 clock4(B[1]);

system_clock #100 clock5(B[0]);

mux hi (out[2], A[2], B[2], SEL);

mux2 lo (out[1:0], A[1:0], B[1:0], SEL);

endmodule

module mux(OUT, A, B, SEL);

output OUT;

input A,B,SEL;

not I5 (sel_n, SEL) ;

and I6 (sel_a, A, SEL);

and I7 (sel_b, sel_n, B);

or I4 (OUT, sel_a, sel_b);

endmodule

module mux2(OUT, A, B, SEL);

output [1:0] OUT;

input [1:0] A,B;

input SEL;

mux hi (OUT[1], A[1], B[1], SEL);

mux lo (OUT[0], A[0], B[0], SEL);

endmodule

module system_clock(clk);

parameter PERIOD=100;

output clk;

reg clk;

initial clk=0;

always

begin

#(PERIOD/2) clk=~clk;

end

always@(posedge clk)

if($time>6500)$stop;

endmodule